# Q1900

### VITERBI/TRELLIS DECODER

#### **FEATURES**

- Viterbi Mode Rates <sup>1</sup>/<sub>3</sub>, <sup>1</sup>/<sub>2</sub>, <sup>3</sup>/<sub>4</sub> and <sup>7</sup>/<sub>8</sub>

- Trellis Mode Rates 2/3 and 3/4

- Full Duplex Encode and Decode in Both Viterbi and Trellis Modes

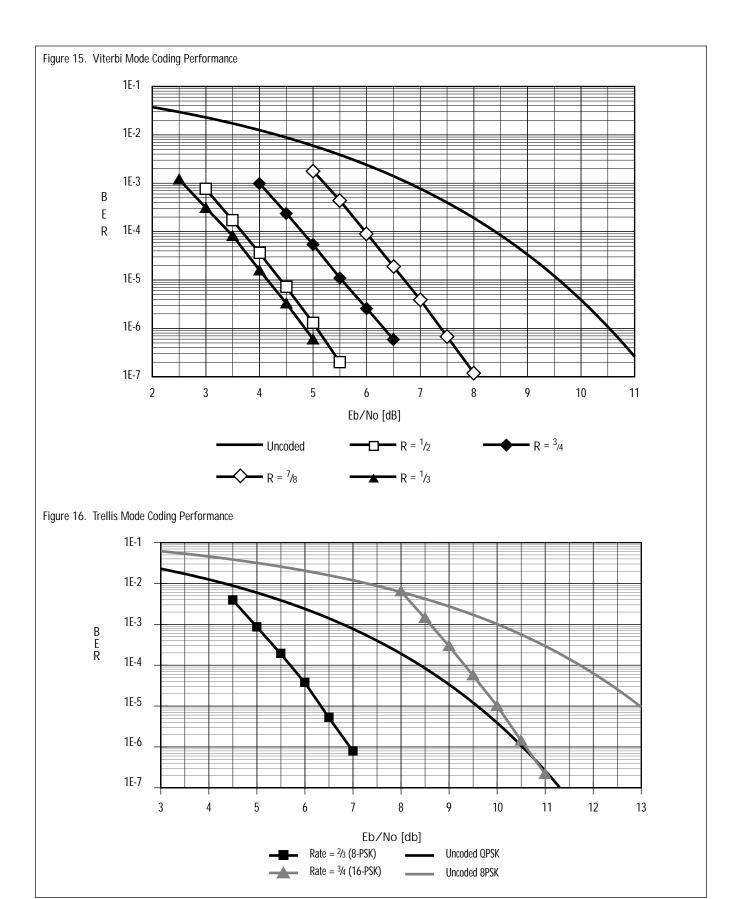

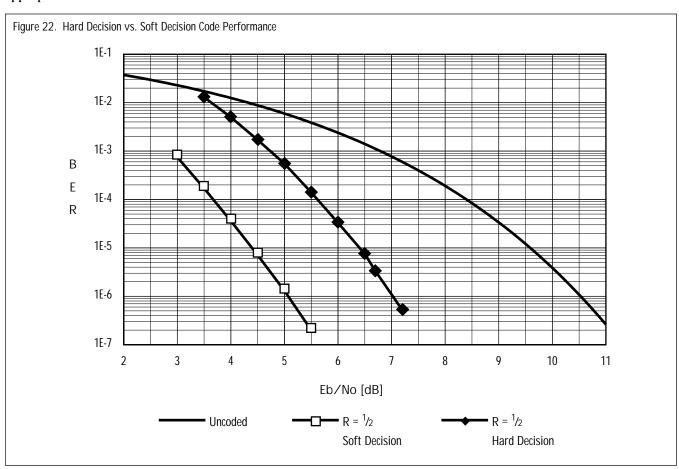

- Large Coding Gains at Eb/No of 10-5

- 5.5 dB for Rate 1/3 Viterbi Decoding

- 5.2 dB for Rate ½ Viterbi Decoding

- 3.2 dB for Rate <sup>2</sup>/<sub>3</sub> Trellis Decoding

- 3.1 dB for Rate <sup>3</sup>/<sub>4</sub> Trellis Decoding

- Automatic Phase Synchronization for BPSK and QPSK in Viterbi Mode and for 8-PSK and 16-PSK in Trellis Mode

- Data Rates up to 25 Mbps for Viterbi Mode and 75 Mbps (16-PSK) for Trellis Mode

- 3-Bit Soft Decision or 1-Bit Hard Decision Decoder Inputs for Viterbi Mode

- Viterbi Mode On-chip Channel Bit Error Rate (BER) Monitor

- Easy Implementation of Additional Code Rates

- Processor Inferface Simplifies Control and Status

- Low-power CMOS Implementation

- Viterbi Mode Complies with INTELSAT IESS-308 and INTELSAT IESS-309

- Standard 84-Pin PLCC or 100-Pin VTQFP Package

### **CONTENTS**

| FEATURES                                                              | 1-1  |

|-----------------------------------------------------------------------|------|

| GENERAL DESCRIPTION                                                   | 1-4  |

| THEORY OF OPERATION                                                   | 1-6  |

| Encoding                                                              | 1-6  |

| Viterbi Mode                                                          | 1-6  |

| Trellis Mode                                                          | 1-10 |

| Decoding                                                              | 1-11 |

| Viterbi Mode                                                          | 1-11 |

| Trellis Mode                                                          | 1-11 |

| Memory Chainback                                                      | 1-15 |

| Viterbi Mode                                                          | 1-15 |

| Trellis Mode                                                          | 1-15 |

| Clocking Scheme                                                       | 1-15 |

| Coding Performance                                                    | 1-15 |

| Viterbi Mode                                                          | 1-15 |

| Trellis Mode                                                          | 1-15 |

| Channel Bit Error Rate Monitor                                        | 1-17 |

| Viterbi Mode                                                          | 1-17 |

| Trellis Mode                                                          | 1-18 |

| Normalization Rate Monitor Operation (Synchronization Status Monitor) | 1-19 |

| Viterbi Mode Example                                                  | 1-20 |

| Trellis Mode Example                                                  | 1-20 |

| Phase Ambiguity Resolution                                            | 1-20 |

| Viterbi Mode                                                          | 1-21 |

| Trellis Mode                                                          | 1-21 |

| Input Data Formats                                                    | 1-21 |

| Viterbi Mode                                                          | 1-21 |

| Trellis Mode                                                          | 1-22 |

| Reset Circuit Operation                                               | 1-23 |

| Viterbi Mode and Trellis Mode                                         | 1-23 |

| Device Throughput Delay                                               | 1-23 |

| Viterbi Mode                                                          | 1-23 |

| Trellis Mode                                                          | 1-23 |

| Direct vs. Parinharal Data Moda                                       | 1_23 |

| MODES OF OPERATION                                           | 1-24 |

|--------------------------------------------------------------|------|

| Parallel vs. Serial Data Modes                               | 1-24 |

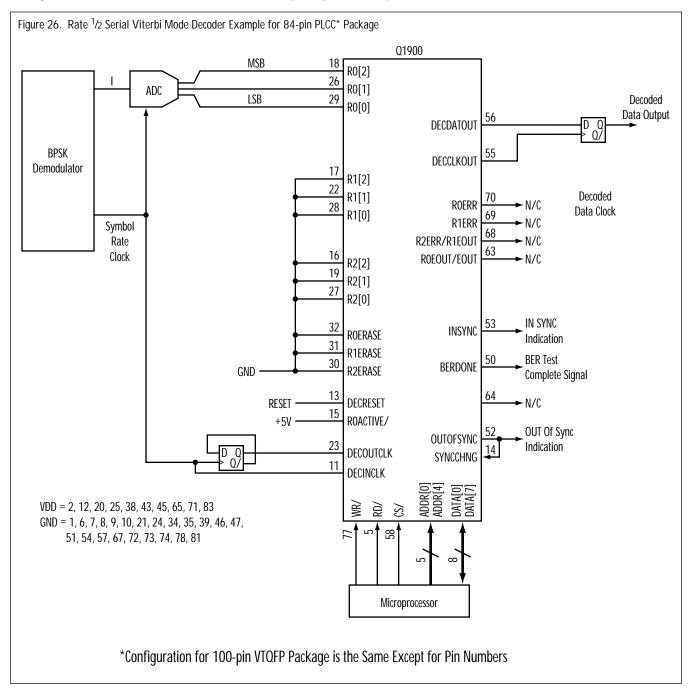

| Rate ½ Serial Viterbi Operation                              | 1-27 |

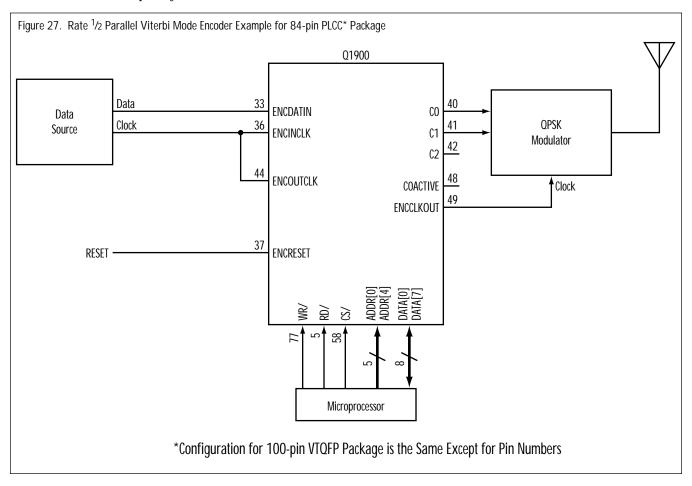

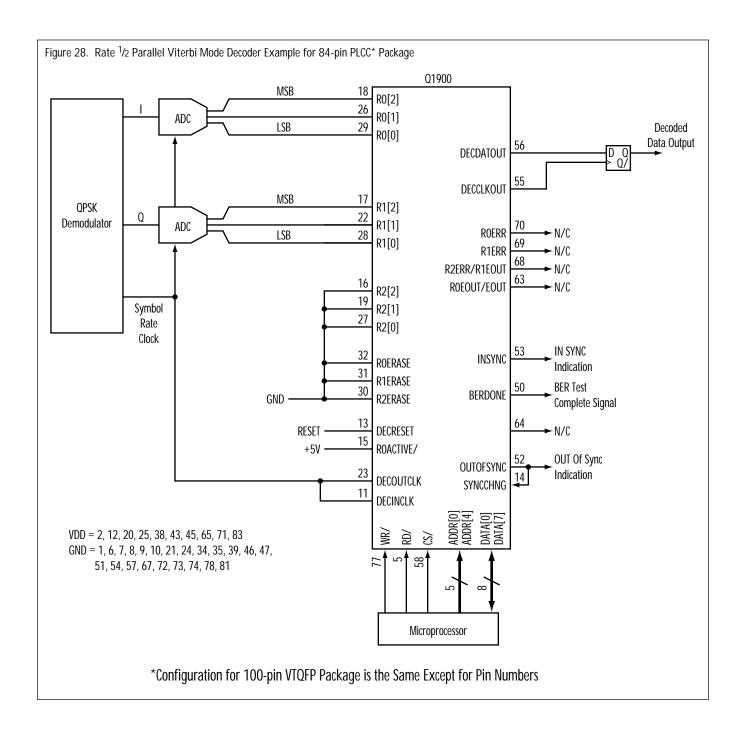

| Rate ½ Parallel Viterbi Operation                            | 1-29 |

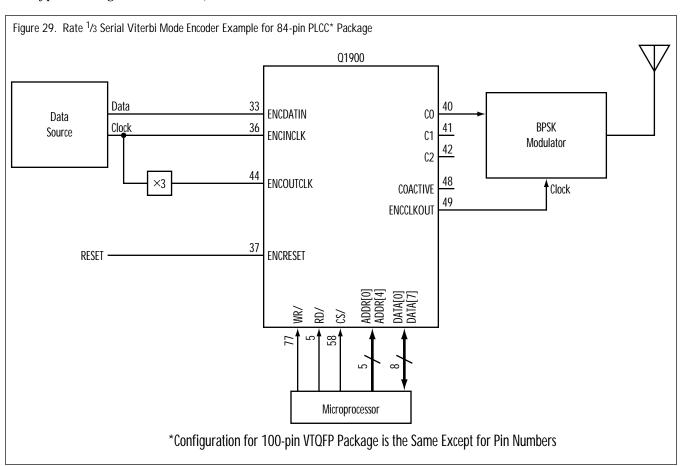

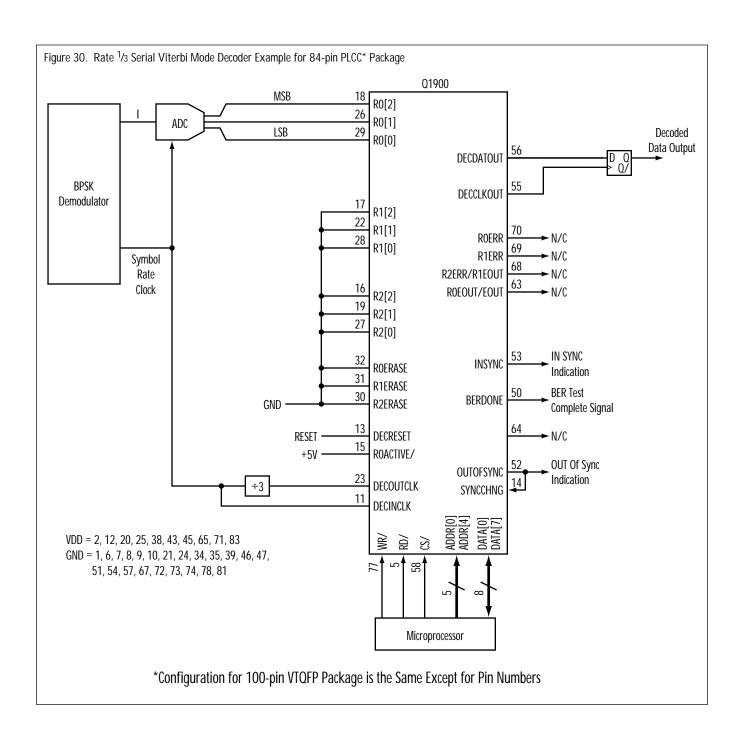

| Rate <sup>1</sup> / <sub>3</sub> Serial Viterbi Operation    | 1-33 |

| Rate <sup>1</sup> / <sub>3</sub> Parallel Viterbi Operation  | 1-36 |

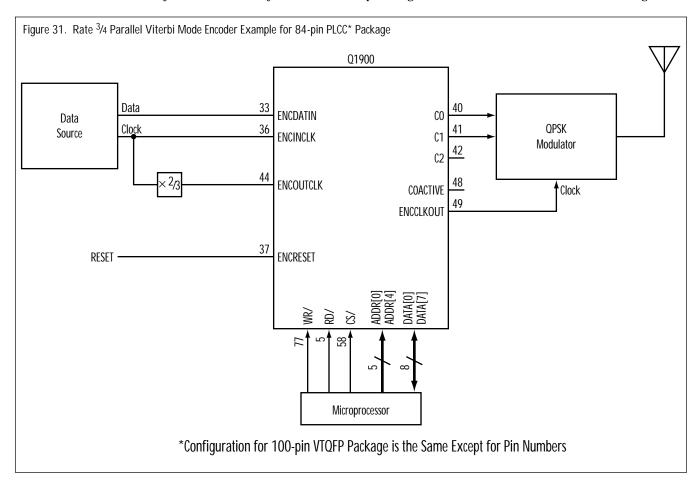

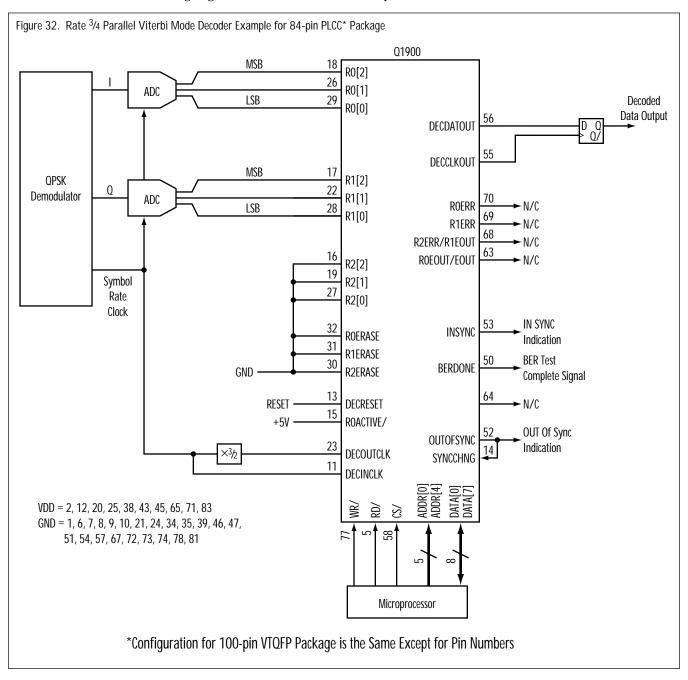

| Rate <sup>3</sup> / <sub>4</sub> Parallel Viterbi Operation  | 1-37 |

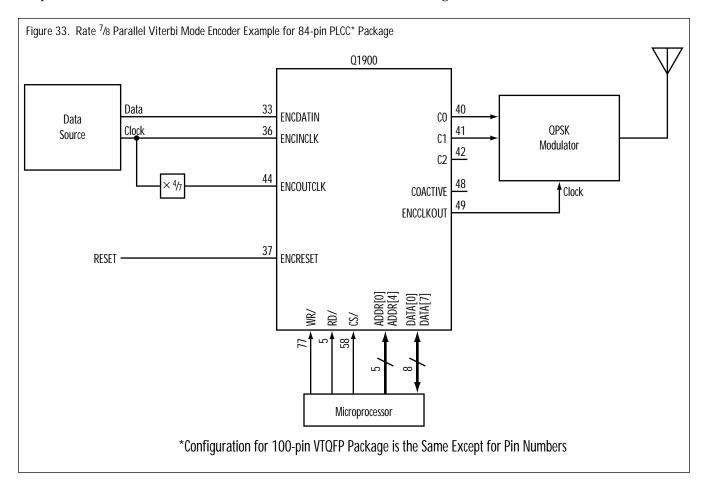

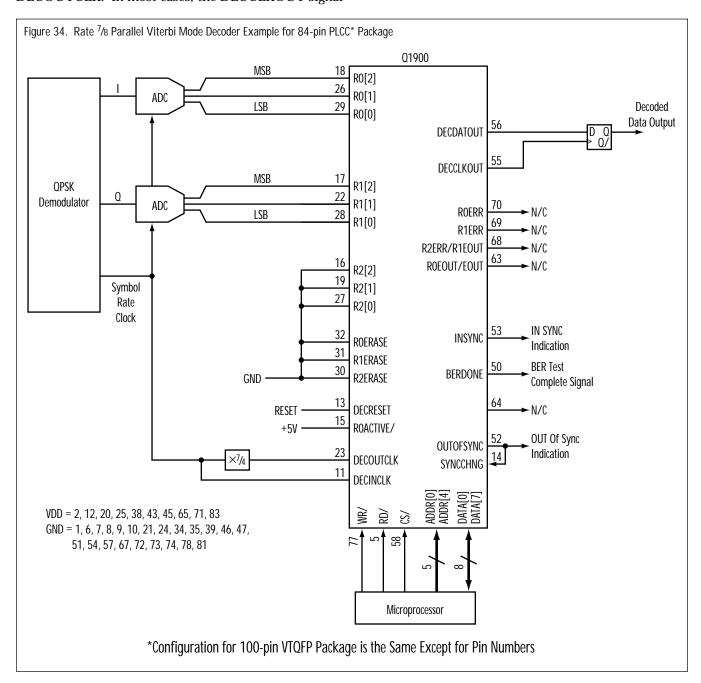

| Rate <sup>7</sup> /8 Parallel Viterbi Operation              | 1-40 |

| Higher Viterbi Code Rate Operation Using External Puncturing | 1-42 |

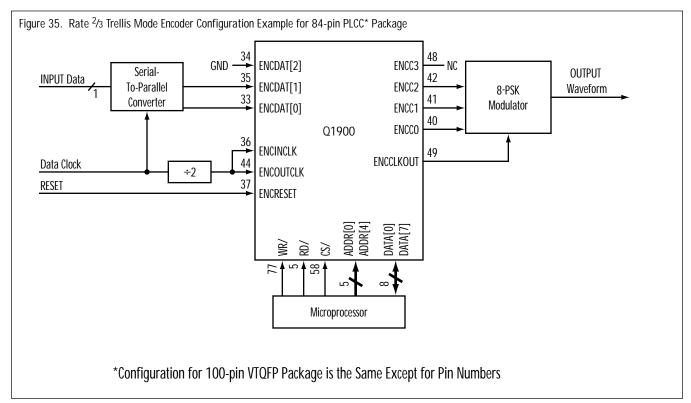

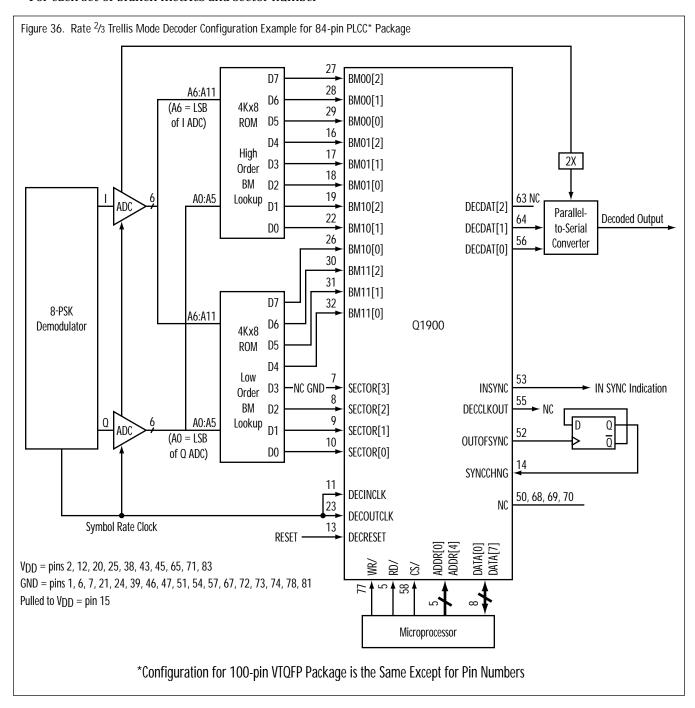

| Rate <sup>2</sup> / <sub>3</sub> 8-PSK Trellis Operation     | 1-43 |

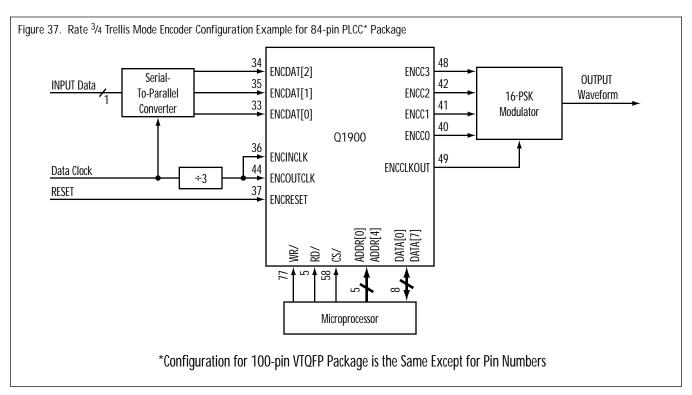

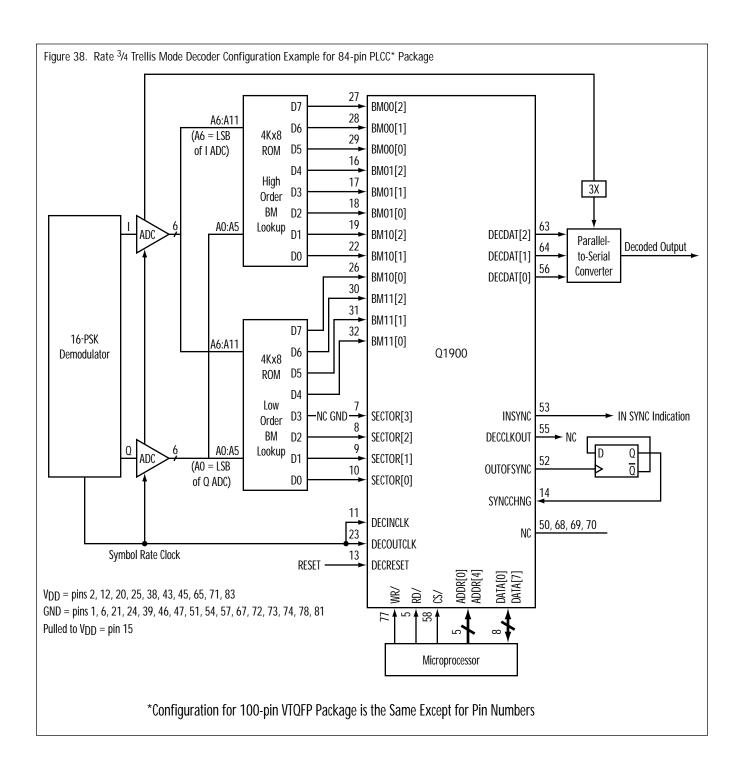

| Rate 3/4 16-PSK Trellis Operation                            | 1-46 |

| TECHNICAL SPECIFICATION                                      | 1-49 |

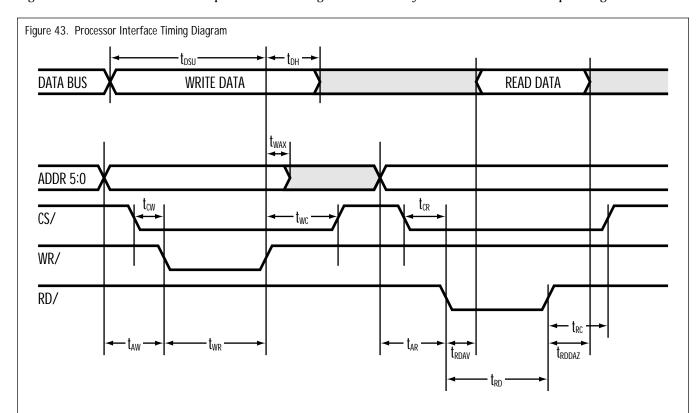

| Processor Interface                                          | 1-49 |

| Read Register                                                | 1-49 |

| Write Register                                               | 1-49 |

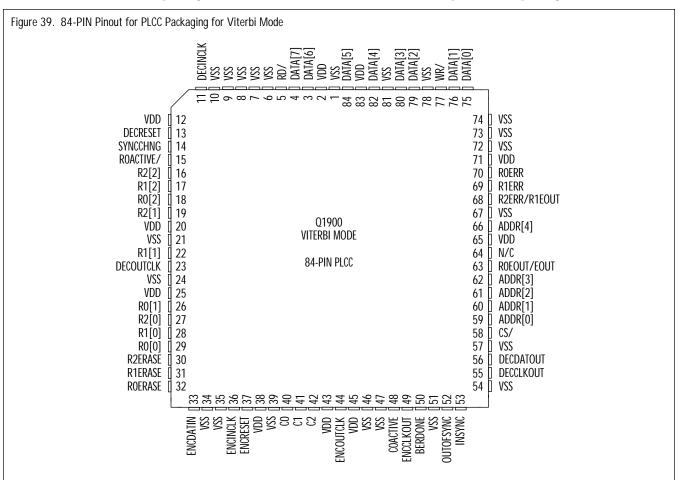

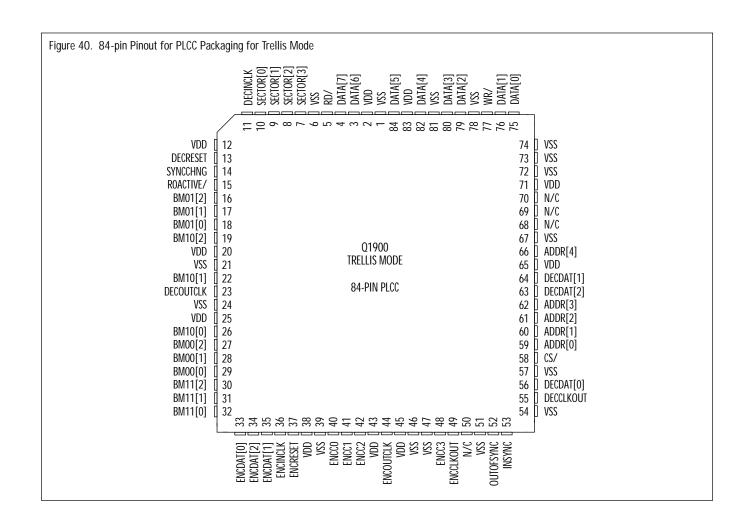

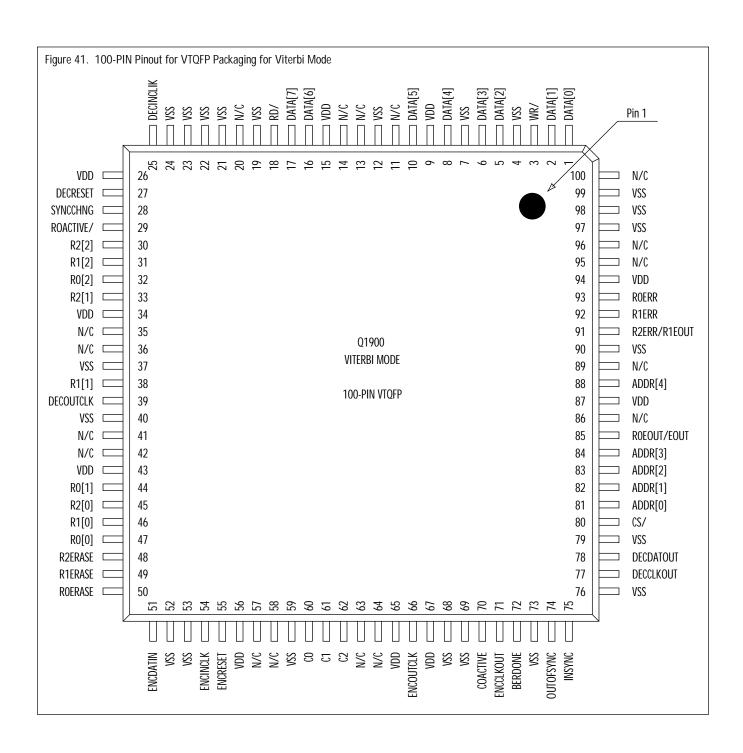

| Pin Descriptions                                             | 1-62 |

| ELECTRICAL SPECIFICATIONS                                    | 1-70 |

| Absolute Maximum Ratings                                     | 1-70 |

| DC ELECTRICAL CHARACTERISTICS                                | 1-71 |

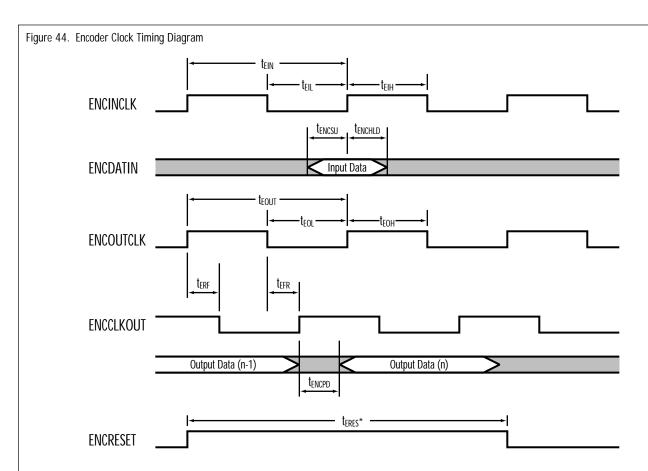

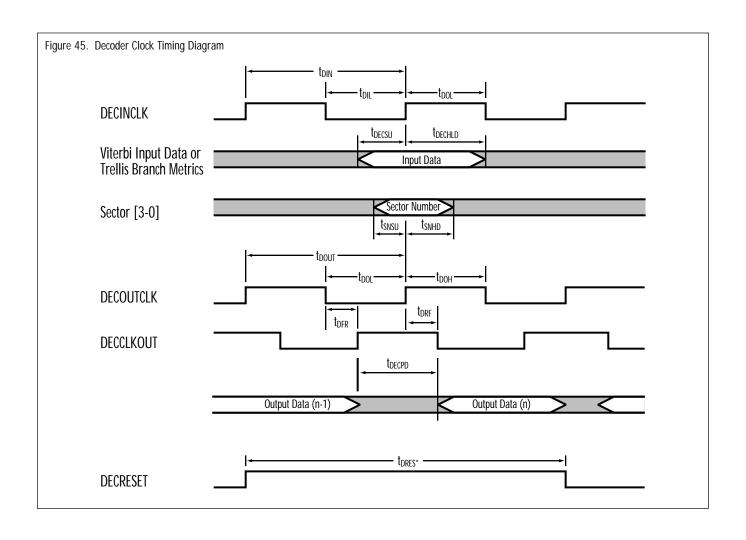

| TIMING CHARACTERISTICS                                       | 1-72 |

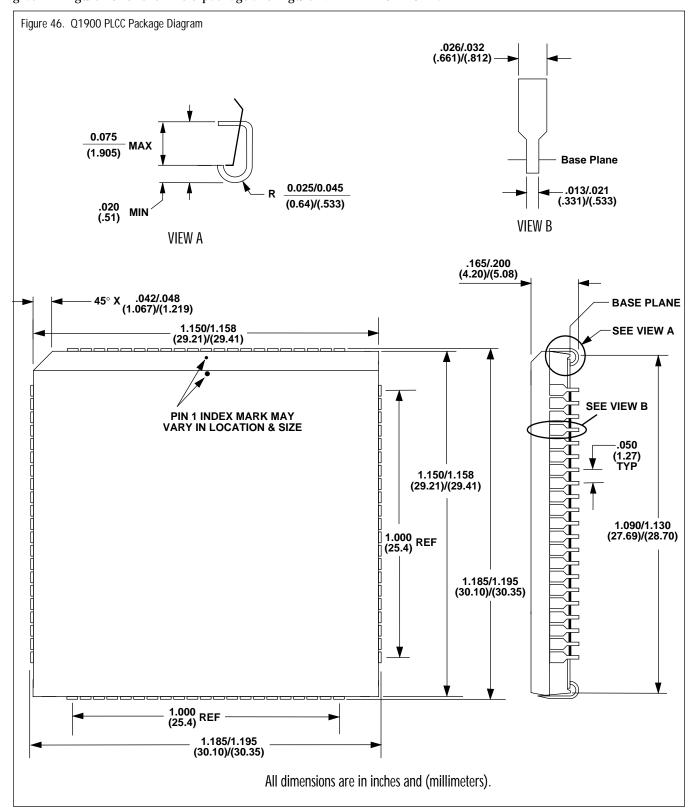

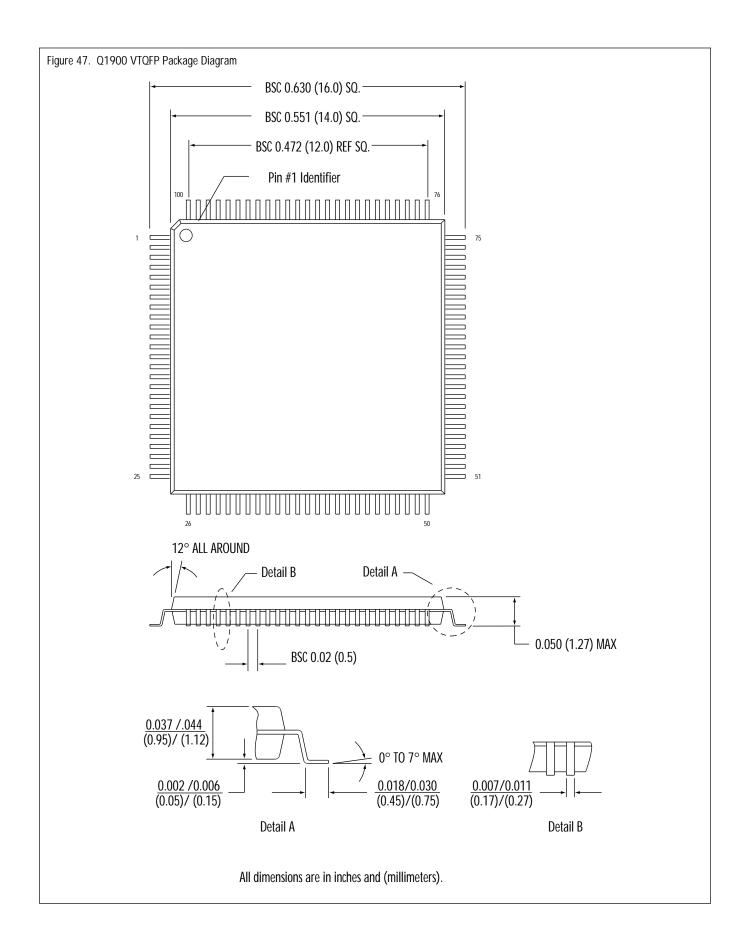

| PACKAGES                                                     | 1-76 |

#### GENERAL DESCRIPTION

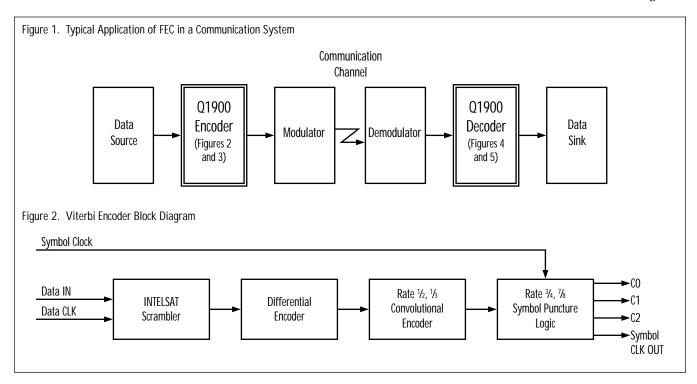

Forward Error Correction (FEC) improves the bit error rate (BER) performance of power-limited and/or bandwidth-limited channels by adding structured redundancy to the transmitted data. The type of additive noise experienced on the channel determines the class of FEC used on the channel. Tree codes are used for channels with Additive White Gaussian Noise (AWGN) and block codes are used for channels with additive burst noise. The Q1900 is based on a k=7Viterbi decoder tree code, optimizing performance over channels with AWGN. The Q1900 supports encoding and decoding for Viterbi and Trellis Modes of operation. The Viterbi Mode is typically used for systems that are power-limited but not bandwidth-limited. The standard modulation types are Binary Phase Shift Keying (BPSK) and Quadrature Phase Shift Keying (QPSK). Trellis Mode is typically used for systems that are both power-limited and bandwidth-limited. The standard modulation types are 8-PSK and 16-PSK. Figure 1 shows a typical application of FEC techniques in a communication system.

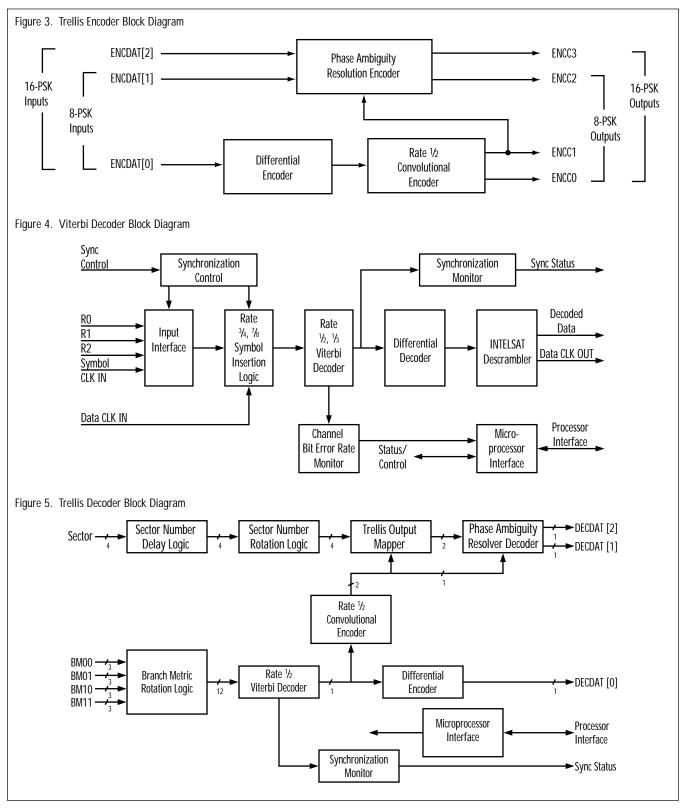

Figures 2 and 3 show the encoder block diagrams for the Viterbi and Trellis Modes. Figures 4 and 5 show the decoder block diagrams for the Viterbi and Trellis Modes. The encoders are both based on a k=7

convolutional encoder and the decoders are both based on a k=7 Viterbi decoder.

The Viterbi Mode supports four code rates: 1/3, 1/2, 3/4 and  $\frac{7}{8}$ . Additional code rates can be supported with external circuitry. The Viterbi Mode also supports built-in phase synchronization for standard BPSK, QPSK, and Offset Quadrature Phase Shift Keying (OQPSK) modulation techniques. Either 1 bit harddecision or 3 bit soft-decision input data is supported. The Viterbi Mode also includes two powerful built-in techniques for monitoring synchronization status as well as performing channel BER measurements.

The Trellis Mode supports two codes rates: 2/3 for 8 PSK and <sup>3</sup>/<sub>4</sub> for 16 PSK. The Trellis Mode also supports built-in phase synchronization for 8-PSK and 16-PSK. The Viterbi and Trellis Modes include a processor interface to facilitate control and status monitoring functions while keeping device pinout to a minimum.

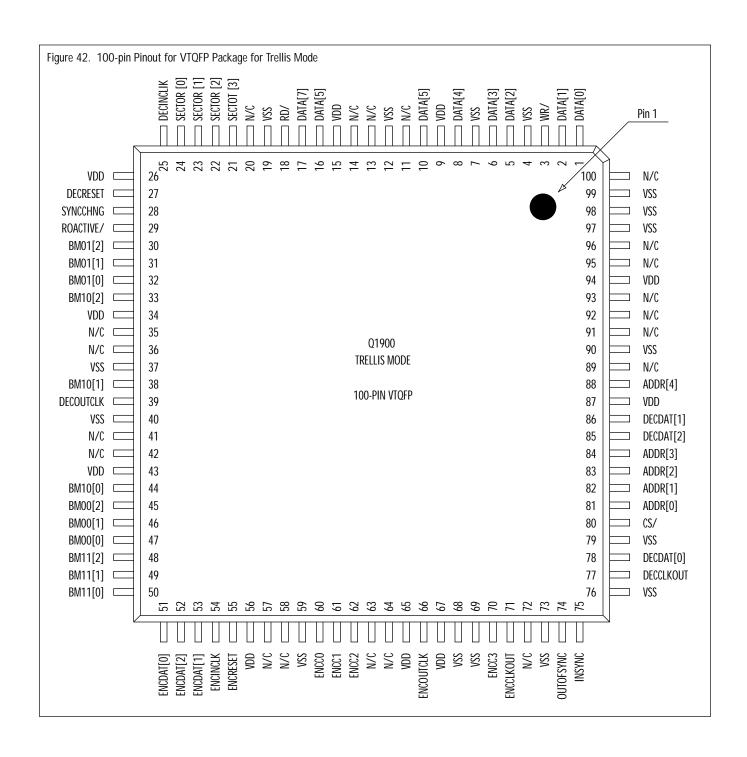

The Q1900 is packaged in a 84-pin PLCC package or a 100-pin VTQFP package and is implemented in fully static CMOS logic to reduce power consumption. It also uses fully parallel circuit architecture to negate the requirement for a higher speed computation clock.

The Q1900 is well suited for many commercial satellite communication networks, including INMARSAT and INTELSAT. The low-cost and high

http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556

performance of the Q1900 make it ideal for FEC requirements in systems such as direct broadcast satellites (DBS), microwave point-to-point data links, very small aperture terminals (VSAT), digital modems,

digital video transmission systems, high-speed data modems and military and NASA communication systems.

### THEORY OF OPERATION **ENCODING**

#### VITERBI MODE

The transformation from information bit to code word for the Viterbi Mode is shown in Figure 2. The number of functions involved in this process can range from one to four depending on which functions are enabled.

The first function is an INTELSAT specified scrambling algorithm. This algorithm is a slight modification to the CCITT V.35 algorithm. The details of this algorithm are described in the Data Scrambling Applications Note section of this data book. Scrambling is used in many communications systems to guarantee minimum transition densities in the transmitted signal for purposes such as timing loop synchronization.

A system consideration when using data scrambling is multiplication of output bit errors. Because the data

Figure 6. Differential Encoder Mod 2 Adder Coded Output Input Data 1 Bit

Delay

scrambler output bits are affected by several input bits, error multiplication occurs. If the Viterbi decoder incorrectly decodes a bit and this single bit is input into the descrambler, it can generate up to three output errors. However, in actuality the error multiplication is a factor of 1.5 to 2. This equates to a coding gain loss of only 0.2 to 0.3 dB.

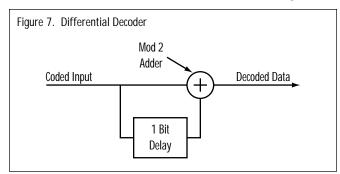

The second function is a differential encoder. The block diagrams for the differential encoder and decoder are shown in Figures 6 and 7. The differential encoder and decoder are used to resolve inverted data. The differential encoder actually transforms the input data stream into an indication of transitions rather than 1's or 0's. If a 0 is input into the encoder, the output stays the same. If a 1 is input, the output transitions either 0 to 1 or 1 to 0.

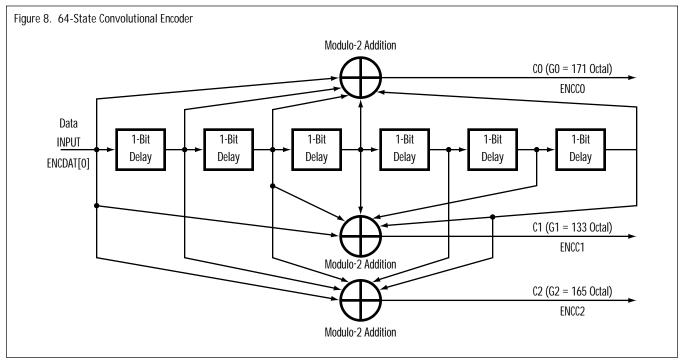

The third function is the industry standard k=7 rate 1/2 or rate 1/3 convolutional encoder, shown in Figure 8.

http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005

Fax: (619) 658-1556

It is used to encode the ENCDAT[0] input bit into two or three output bits ENCC0, ENCC1 and ENCC2.

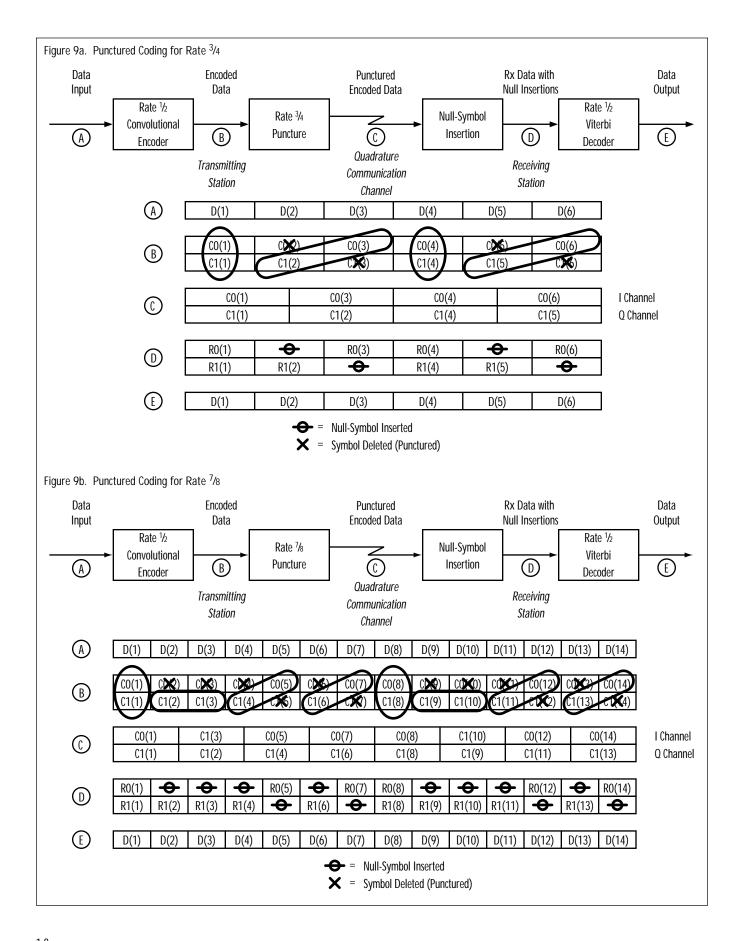

The fourth function is the puncture logic. This step punctures the rate  $^{1}\!/_{2}$  data into either rate  $^{3}\!/_{4}$  or rate  $^{7}\!/_{8}$ . Figures 9a and 9b show how rate  $^{1}\!/_{2}$  data is punctured into rate  $^{3}\!/_{4}$  rate  $^{7}\!/_{8}$ . The input data is encoded with a rate  $^{1}\!/_{2}$  encoder (B). Then certain bits of the rate  $^{1}\!/_{2}$  encoded data are punctured, or deleted, and not transmitted (C). For rate  $^{3}\!/_{4}$ , two out of six bits from the rate  $^{1}\!/_{2}$  encoder are deleted in a repeating pattern. Thus, for every three input bits, only four encoded bits are actually transmitted making this a rate  $^{3}\!/_{4}$  code. For rate  $^{7}\!/_{8}$ , six out of fourteen bits from the rate  $^{1}\!/_{2}$  encoder are deleted in a repeating pattern. Thus, for every seven input bits, only eight encoded bits are actually transmitted making this a rate  $^{7}\!/_{8}$  code.

At the receiver, the punctured bits are replaced with null bits prior to decoding with the rate  $^{1}/_{2}$  decoder (D). Insertion of the null bits is done automatically if the Q1900 is programmed for rate  $^{3}/_{4}$  or  $^{7}/_{8}$ . For punctured rates other than  $^{3}/_{4}$  and  $^{7}/_{8}$ , insertion of the null bits is done externally by asserting the erase input pins as appropriate for R0, R1, or R2. The decoder treats null bits as an input which is neither a received "1" nor "0", but is exactly between the "1" and "0".

The coding performance of a punctured rate  $\frac{3}{4}$  code is equivalent to the coding performance of a classic non-punctured rate  $\frac{3}{4}$  code. The major advantage of punctured coding with a standard rate convolution

encoder (1/2 or 1/3) is that a single code rate decoder can decode a wide range of codes. Specifically, any code rate of the form (n-1)/n can be efficiently implemented with this structure. Of course, the best performance is achieved with certain puncture patterns. The best punctured codes have been researched and are shown in Figure 10 for rates from ½ through 16/17. The chainback depth must increase as the code rate increases. A chainback memory depth of 35-40 states is adequate for rate ½ decoding. However, rate ¾ decoders require memory depths of at least 70 states, and rate \(^{7}\)8 requires chainback depth of more than 90 states. The Q1900 decoder uses a minimum chainback memory depth of 96 states for puncture coding. Therefore, it is very effective at decoding code rates up to  $\frac{7}{8}$ . Operation with code rates higher than  $\frac{7}{8}$  will result in a minor performance degradation in the coding gain when compared to the theoretical best.

During punctured coding, the decoder must synchronize the null symbol insertion pattern of the decoder to the symbol puncture pattern of the encoder. The Q1900 performs all the necessary symbol puncture (encoder), null symbol insertion (decoder) and synchronization functions required to implement rates <sup>3</sup>/<sub>4</sub> and <sup>7</sup>/<sub>8</sub>. The decoder also includes First-In-First-Out (FIFO) circuits which ease the frequent requirement of punctured code systems to re-align the punctured encoded stream to a channel clock, which is a non-integer multiple of the information data rate.

Figure 10. Best Punctured Code Patterns

| Code Rate                     | Puncture Pattern (0 = Deleted Code Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/2                           | CO: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| '72                           | C1: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <sup>2</sup> / <sub>3</sub>   | CO: 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 73                            | C1: 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3/4*                          | co: (1) 9 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 74                            | c1: \1/(1./0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <sup>4</sup> / <sub>5</sub>   | CO: 1 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 75                            | C1: 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <sup>5</sup> / <sub>6</sub>   | CO: 1 0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 70                            | C1: 1 1 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6/7                           | CO: 1 0 0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11                            | C1: 1 1 1 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <sup>7</sup> /8*              | co: (1) o_o (2) (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 70                            | C1: \J\(\frac{1}{\dagger}\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagger\dagg |

| <sup>11</sup> / <sub>12</sub> | CO: 1 0 0 0 1 0 0 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 712                           | C1: 1 1 1 1 0 1 1 1 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <sup>12</sup> / <sub>13</sub> | CO: 10000001010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| /13                           | C1: 1 1 1 1 1 1 1 0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <sup>15</sup> / <sub>16</sub> | CO: 100110100101101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 710                           | C1: 1 1 1 0 0 1 0 1 1 0 1 0 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <sup>16</sup> / <sub>17</sub> | CO: 101010110111010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| /1/                           | C1: 1 1 0 1 0 1 0 0 1 0 0 0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

<sup>\*</sup> Two code bit groupings are shown for operation with code rates  $^{3}\!/_{4}$  and  $^{7}\!/_{8}$  in Parallel Data Mode. CO and C1 code bits are output on the CO and C1 signals, respectively, except for the second symbol in rate  $^{7}\!/_{8}$  pattern. In that case, the second of the two C1 code bits is output on the CO signal.

#### TRELLIS MODE

The transformation from information bits to code words for rate \$\frac{2}{3}\$ 8-PSK and rate \$\frac{3}{4}\$ 16-PSK is a three-step process (Figure 3). First, the ENCDAT[0] data bit is differentially encoded, if differential encoding is enabled. Next, the industry standard k=7 rate \$\frac{1}{2}\$ convolutional encoder is used to encode the ENCDAT[0] input bit into two output bits, ENCC0 and ENCC1. The output bits, ENCC0 and ENCC1, become the Least Significant Bits (LSBs) of the transmitted phase. The third step applies phase ambiguity resolution encoding to the ENCDAT[1] bit for \$\frac{2}{3}\$ 8-PSK and to the ENCDAT[1] and ENCDAT[2] bits for \$\frac{3}{4}\$ 16-PSK.

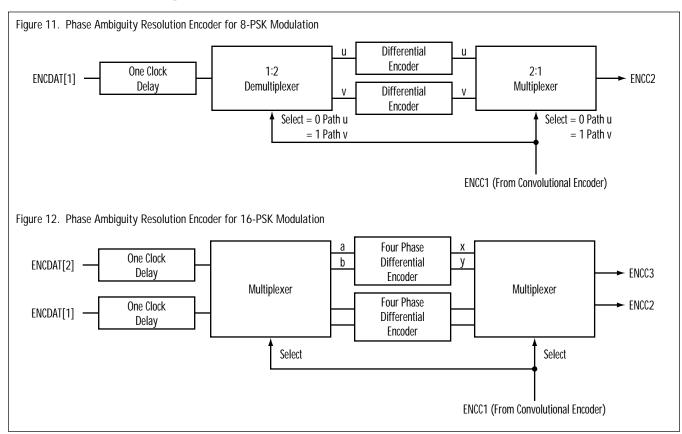

The encoder phase ambiguity resolution functions for 8-PSK and 16-PSK are shown in Figures 11 and 12. The encoder phase ambiguity function uses the convolutional encoder output, ENCC1, to select one of two differential encoders for ENCDAT[1] (8-PSK), and for ENCDAT[1] and ENCDAT[2] (16-PSK). Table 1 shows the states of the four-phase differential encoder.

| PRESEN | T INPUT | LAST   | INPUT  | OUT  | PUT  |

|--------|---------|--------|--------|------|------|

| a(n)   | b(n)    | a(n-1) | b(n-1) | x(n) | y(n) |

| 0      | 0       | 0      | 0      | 0    | 0    |

| 0      | 1       | 0      | 0      | 0    | 1    |

| 1      | 0       | 0      | 0      | 1    | 0    |

| 1      | 1       | 0      | 0      | 1    | 1    |

| 0      | 0       | 0      | 1      | 0    | 1    |

| 0      | 1       | 0      | 1      | 1    | 1    |

| 1      | 0       | 0      | 1      | 0    | 0    |

| 1      | 1       | 0      | 1      | 1    | 0    |

| 0      | 0       | 1      | 0      | 1    | 0    |

| 0      | 1       | 1      | 0      | 0    | 0    |

| 1      | 0       | 1      | 0      | 1    | 1    |

| 1      | 1       | 1      | 0      | 0    | 1    |

| 0      | 0       | 1      | 1      | 1    | 1    |

| 0      | 1       | 1      | 1      | 1    | 0    |

| 1      | 0       | 1      | 1      | 0    | 1    |

| 1      | 1       | 1      | 1      | 0    | 0    |

Table 1. Four-Phase Differential Encoder State Table

#### **DECODING**

While the implementation of the convolutional encoder functions for the Viterbi Mode and the Trellis Mode are straightforward and simple, the decoding of the data stream at the receiving node is complex.

#### VITERBI MODE

Viterbi decoding consists of three fundamental steps. The first step is to generate a set of correlation measurements, known as branch metrics, for each "m" grouping of code words input from the communication channel, where "m" is 2 for rate ½ codes, 3 for rate ½ codes, etc. These branch metric values indicate the correlation between the received code words and the 2"m" possible code word combinations.

The Viterbi decoder determines the state of the 7-bit memory at the encoder using a maximum likelihood technique. Once the value of the encoder memory is determined, the original information is known since the encoder memory is simply the information that has been stored. To determine the encoder state, the second step in the Viterbi algorithm generates a set of  $2^{k-1}$  state metrics, where "k" is the constraint length (k=7 for the Q1900) which measures the occurrence probability for each of the  $2^{k-1}$  possible encoder memory states. As the state metrics are computed, a binary decision is formed for each of the  $2^{k-1}$  possible states, determining the probable path taken to arrive at that particular state. These binary decisions are stored in the path memory.

Step three computes the decoded output data. The path from the current state to some point in a finite past state is traced back by chaining the binary decisions stored in the path memory (step 2). The effects caused by noise are mitigated as paths to the correct result converge after some history. The greater the depth of the chainback process, the more likely that the final decoded result is error-free. As a result, higher code rates and constraint lengths require longer chainback depth for best performance.

#### TRELLIS MODE

The Trellis Mode also uses an industry standard k=7 Viterbi decoder along with supplementary circuitry to decode the trellis encoded data. This technique is called Pragmatic Trellis Coded Modulation (PTCM) decoding (U.S. patent No. 5,469,452 - foreign patents issued and pending).

Fundamentally, PTCM decoding consists of three steps. First, the received symbol or phase angle is converted to four branch metrics and a sector number. Second, the branch metrics are processed with a standard k=7 Viterbi decoder to decode the least significant output bit, DECDAT[0]. The third step decodes the most significant output bit(s) DECDAT[1] for 8-PSK and DECDAT[1] and DECDAT[2] for 16-PSK. The three steps are described in detail in the following paragraphs.

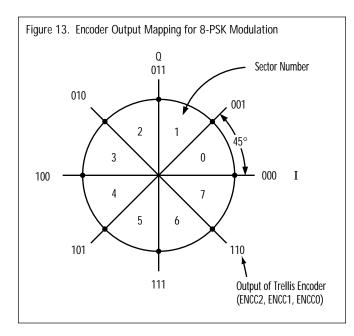

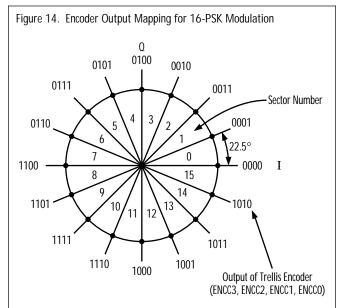

In the first step, the received phase angle is converted to four branch metrics and a sector number with an external lookup table. The branch metrics are based on the Euclidean distance of the received phase with respect to the four closest transmitted phase points. The branch metric and sector number for 8-PSK are given in Table 2. The branch metrics and sector number for 16-PSK are given in Tables 3a and 3b. The sector number tells the decoder on which portion of the I-Q plane the symbol was received. For 8-PSK modulation, sector numbers are assigned by dividing the signal constellation into eight equal sectors (Figure 13). Likewise, for 16-PSK modulation, the signal constellation is divided into sixteen equal sectors (Figure 14). The actual value input into the Q1900 PTCM decoder is the binary representation of the sector number. Note: A sector is defined from a signal point counterclockwise to the border of the next signal point. For example, sector 2 for 8-PSK modulation begins at the phase point 011 (90°) but ends just before phase point 010 (135°).

In the second step of the decoding process, the PTCM decoder processes the branch metrics with the standard k=7 Viterbi decoder algorithm. The decoded output DECDAT[0] becomes the least significant output bit.

The third step re-encodes the DECDAT[0] data bit to generate the best possible estimate of the transmitted LSBs, ENCC0 and ENCC1. For each combination given of ENCC0 and ENCC1, there are 2 possible transmitted

6455 Lusk Boulevard, San Diego, CA 92121-2779, USA Forward Error Correction Products Data Book, 80-24128-1, 2/97 Data Subject to Change Without Notice

phase angles for 8-PSK and 4 possible transmitted phase angles for 16-PSK. For example, if the received LSB is equal to 01, this corresponds to 45° or 225° for 8-PSK and to 22.5°, 112.5°, 202.5° and 292.5° for 16-PSK. To determine the MSBs, the received sector number is compared to the 2 or 4 possible phase angles. The phase angle closest to the sector number is chosen as the transmitted phase.

For example, if the received signal has a phase angle of 100° for 8-PSK, this corresponds to a sector number of 2. See Figure 13. If the re-encoded bit provides estimates of ENCC1=0 and ENCC0=1, the two possible transmitted phase points are 001 and 101. Since the received phase of 100° is located in a sector that is closer to phase point 001 than to phase point 101, the DECDAT[1] is determined to be 0.

Table 2. 8-PSK Modulation Phase to Branch Metric Conversion

| Phase                       | B00<br>(OCT) | B01<br>(OCT) | B11<br>(OCT) | B10<br>(OCT) | Sector<br>Number | Phase                       | B00<br>(OCT) | B01<br>(OCT) | B11<br>(OCT) | B10<br>(OCT) | Sector<br>Number |

|-----------------------------|--------------|--------------|--------------|--------------|------------------|-----------------------------|--------------|--------------|--------------|--------------|------------------|

| $0.0 \le \varphi < 2.8$     | 0            | 4            | 7            | 4            | 0                | $180.0 \le \varphi < 182.8$ | 0            | 4            | 7            | 4            | 4                |

| $2.8 \le \varphi < 8.4$     | 0            | 3            | 7            | 4            | 0                | $182.8 \le \varphi < 188.4$ | 0            | 3            | 7            | 4            | 4                |

| $8.4 \le \phi < 14.1$       | 0            | 2            | 6            | 4            | 0                | $188.4 \le \varphi < 194.1$ | 0            | 2            | 6            | 4            | 4                |

| $14.1 \le \varphi < 19.7$   | 0            | 1            | 5            | 4            | 0                | $194.1 \le \varphi < 199.7$ | 0            | 1            | 5            | 4            | 4                |

| $19.7 \le \varphi < 25.3$   | 0            | 0            | 4            | 4            | 0                | $199.7 \le \varphi < 205.3$ | 0            | 0            | 4            | 4            | 4                |

| $25.3 \le \varphi < 30.9$   | 1            | 0            | 4            | 5            | 0                | $205.3 \le \varphi < 210.9$ | 1            | 0            | 4            | 5            | 4                |

| $30.9 \le \varphi < 36.6$   | 2            | 0            | 4            | 6            | 0                | $210.9 \le \varphi < 216.6$ | 2            | 0            | 4            | 6            | 4                |

| $36.6 \le \varphi < 42.2$   | 3            | 0            | 4            | 7            | 0                | $216.6 \le \varphi < 222.2$ | 3            | 0            | 4            | 7            | 4                |

| $42.2 \le \varphi < 45.0$   | 4            | 0            | 4            | 7            | 0                | $222.2 \le \varphi < 225.0$ | 4            | 0            | 4            | 7            | 4                |

| $45.0 \le \varphi < 47.8$   | 4            | 0            | 4            | 7            | 1                | $225.0 \le \varphi < 227.8$ | 4            | 0            | 4            | 7            | 5                |

| $47.8 \le \varphi < 53.4$   | 4            | 0            | 3            | 7            | 1                | $227.8 \le \varphi < 233.4$ | 4            | 0            | 3            | 7            | 5                |

| $53.4 \le \varphi < 59.1$   | 4            | 0            | 2            | 6            | 1                | $233.4 \le \varphi < 239.1$ | 4            | 0            | 2            | 6            | 5                |

| $59.1 \le \varphi < 64.7$   | 4            | 0            | 1            | 5            | 1                | $239.1 \le \varphi < 244.7$ | 4            | 0            | 1            | 5            | 5                |

| $64.7 \le \varphi < 70.3$   | 4            | 0            | 0            | 4            | 1                | $244.7 \le \varphi < 250.3$ | 4            | 0            | 0            | 4            | 5                |

| $70.3 \le \varphi < 75.9$   | 5            | 1            | 0            | 4            | 1                | $250.3 \le \varphi < 255.9$ | 5            | 1            | 0            | 4            | 5                |

| $75.9 \le \varphi < 81.6$   | 6            | 2            | 0            | 4            | 1                | $255.9 \le \varphi < 261.6$ | 6            | 2            | 0            | 4            | 5                |

| $81.6 \le \varphi < 87.2$   | 7            | 3            | 0            | 4            | 1                | $261.6 \le \varphi < 267.2$ | 7            | 3            | 0            | 4            | 5                |

| $87.2 \le \varphi < 90.0$   | 7            | 4            | 0            | 4            | 1                | $267.2 \le \varphi < 270.0$ | 7            | 4            | 0            | 4            | 5                |

| $90.0 \le \varphi < 92.8$   | 7            | 4            | 0            | 4            | 2                | $270.0 \le \varphi < 272.8$ | 7            | 4            | 0            | 4            | 6                |

| $92.8 \le \phi < 98.4$      | 7            | 4            | 0            | 3            | 2                | $272.8 \le \varphi < 278.4$ | 7            | 4            | 0            | 3            | 6                |

| $98.4 \le \phi < 104.1$     | 6            | 4            | 0            | 2            | 2                | $278.4 \le \varphi < 284.1$ | 6            | 4            | 0            | 2            | 6                |

| $104.1 \le \varphi < 109.7$ | 5            | 4            | 0            | 1            | 2                | $284.1 \le \varphi < 289.7$ | 5            | 4            | 0            | 1            | 6                |

| $109.7 \le \varphi < 115.3$ | 4            | 4            | 0            | 0            | 2                | $289.7 \le \varphi < 295.3$ | 4            | 4            | 0            | 0            | 6                |

| $115.3 \le \varphi < 120.9$ | 4            | 5            | 1            | 0            | 2                | $295.3 \le \varphi < 300.9$ | 4            | 5            | 1            | 0            | 6                |

| $120.9 \le \varphi < 126.6$ | 4            | 6            | 2            | 0            | 2                | $300.9 \le \varphi < 306.6$ | 4            | 6            | 2            | 0            | 6                |

| $126.6 \le \varphi < 132.2$ | 4            | 7            | 3            | 0            | 2                | $306.6 \le \varphi < 312.2$ | 4            | 7            | 3            | 0            | 6                |

| $132.2 \le \varphi < 135.0$ | 4            | 7            | 4            | 0            | 2                | $312.2 \le \varphi < 315.0$ | 4            | 7            | 4            | 0            | 6                |

| $135.0 \le \varphi < 137.8$ | 4            | 7            | 4            | 0            | 3                | $315.0 \le \varphi < 317.8$ | 4            | 7            | 4            | 0            | 7                |

| $137.8 \le \varphi < 143.4$ | 3            | 7            | 4            | 0            | 3                | $317.8 \le \varphi < 323.4$ | 3            | 7            | 4            | 0            | 7                |

| $143.4 \le \varphi < 149.1$ | 2            | 6            | 4            | 0            | 3                | $323.4 \le \varphi < 329.1$ | 2            | 6            | 4            | 0            | 7                |

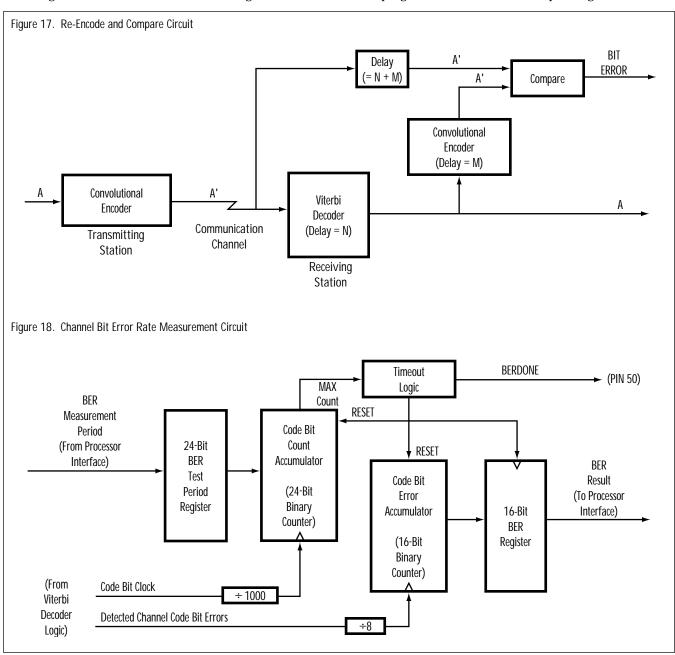

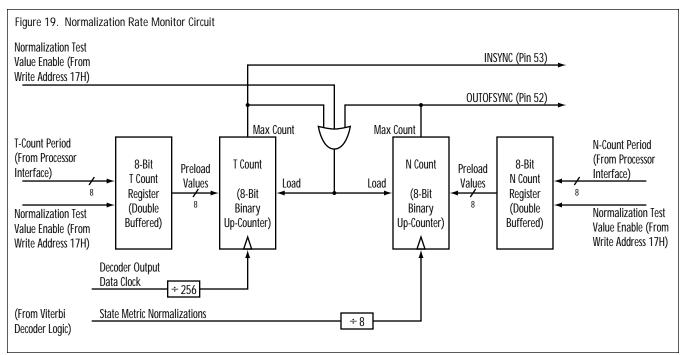

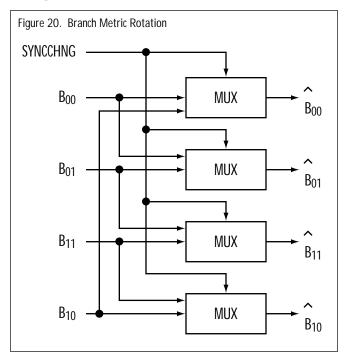

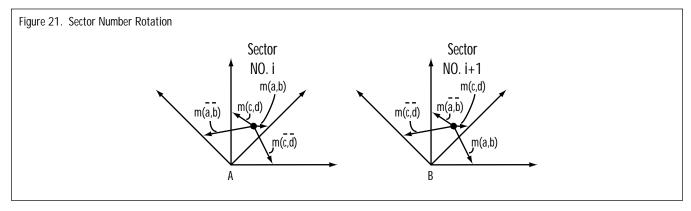

| $149.1 \le \varphi < 154.7$ | 1            | 5            | 4            | 0            | 3                | $329.1 \le \varphi < 334.7$ | 1            | 5            | 4            | 0            | 7                |