# Product Preview QPSK Encoder

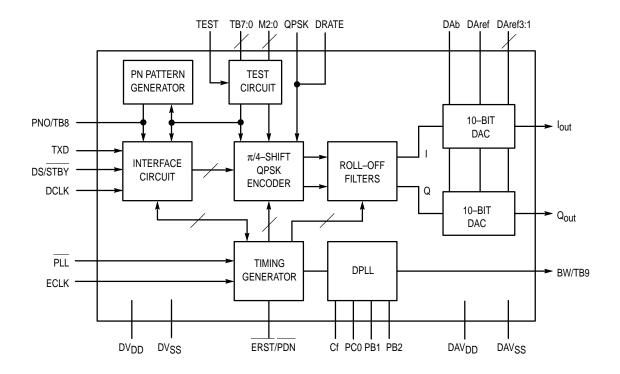

The MC145750 is a silicon gate HCMOS device designed to encode  $\pi/4$ –shift QPSK baseband signals. The device contains two 10–bit DACs for the I/Q signal, Root–Nyquist digital filtering, and burst rising and falling edge processing for digital RF communication equipment. Primary applications for this device are in products that will be used in PHS (384 kbps) and PDC (42 kbps). It will perform up to 800 kbps data rate. It also contains PN511 random pattern generator and timing generator with PLL.

- Root-Nyquist Digital Filtering (Coefficient = 0.5)

- Burst Edge Processing Circuitry (Ramp-Up and -Down)

- Two 10-Bit DACs for I/Q Output

- Operating Voltage Range: 2.7 to 5.5 V

- PN511 Random Pattern Generator

- · Conformance to RCR Standard for PHS, PDC

- Variable Data Transmission Rate up to 800 kbps (VDD = 5 V)

- Timing Generator with PLL

- · QPSK Mode, Burst, and Continuous I/Q Signal Output is Performed

- Companion Device is MRFIC0001

# MC145750

# ORDERING INFORMATION

MC145750VFU VQFP

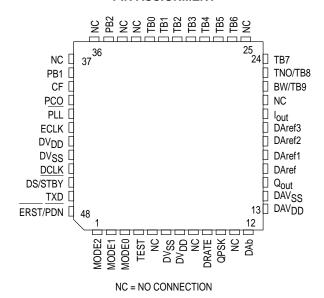

#### **PIN ASSIGNMENT**

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

# **BLOCK DIAGRAM**

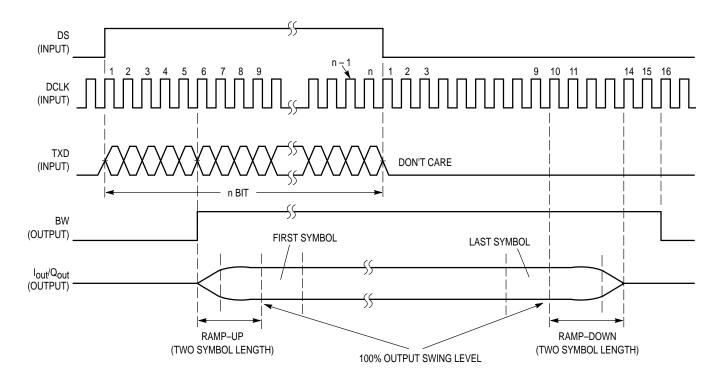

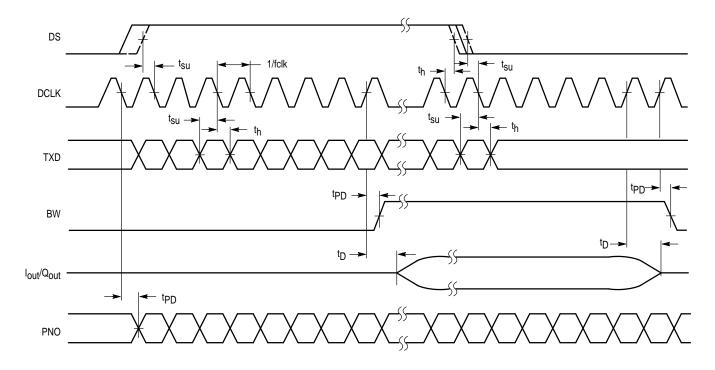

# INPUT/OUTPUT TIMING RELATIONS

MC145750 MOTOROLA

# **MAXIMUM RATINGS**

| Parameter           | Symbol           | Value                          | Unit |

|---------------------|------------------|--------------------------------|------|

| DC Supply Voltage   | V <sub>DD</sub>  | - 0.5 to + 7                   | V    |

| DC Input Voltage    | V <sub>in</sub>  | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| Power Dissipation   | PD               | 500                            | mW   |

| Storage Temperature | T <sub>stg</sub> | - 65 to +150                   | °C   |

# RECOMMENDED OPERATING CONDITIONS

| Parameter                   | Symbol          | Min  | Тур | Max      | Unit |

|-----------------------------|-----------------|------|-----|----------|------|

| DC Supply Voltage           | $V_{DD}$        | 2.7  | 3.3 | 5.5      | V    |

| DC Input Voltage            | V <sub>in</sub> | 0    | _   | $V_{DD}$ | V    |

| Operating Temperature Range | T <sub>A</sub>  | - 20 | 25  | 85       | °C   |

# **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C, TXD = L, Normal Mode)

| Parameter         | s         | Symbol           | Condition            | Min | Тур** | Max  | Unit |

|-------------------|-----------|------------------|----------------------|-----|-------|------|------|

| DC Supply Current |           | I <sub>dd1</sub> | ERST = L             | _   | 0.25  | 0.5  | mA   |

| $V_{DD} = 3 V$    | DRATE = L | I <sub>dd2</sub> | DS = L               | _   | 5.0   | 6.0  |      |

|                   | DRATE = H | I <sub>dd3</sub> |                      | _   | 1.5   | 1.8  |      |

|                   | DRATE = L | I <sub>dd4</sub> | DS = Burst Input*    | _   | 5.0   | 6.0  |      |

|                   | DRATE = H | I <sub>dd5</sub> |                      | _   | 1.5   | 1.8  |      |

|                   | DRATE = L | I <sub>dd6</sub> | DS = Continual Input | _   | 8.0   | 10.0 |      |

|                   | DRATE = H | I <sub>dd7</sub> |                      | _   | 2.0   | 2.6  |      |

| DC Supply Current |           | I <sub>dd1</sub> | ERST = L             | _   | 0.5   | 3.0  | mA   |

| $V_{DD} = 5 V$    | DRATE = L | I <sub>dd2</sub> | DS = L               | _   | 27.0  | 33.0 |      |

|                   | DRATE = H | I <sub>dd3</sub> |                      | _   | 17.0  | 19.0 |      |

|                   | DRATE = L | I <sub>dd4</sub> | DS = Burst Input*    | _   | 30.0  | 33.0 |      |

|                   | DRATE = H | I <sub>dd5</sub> |                      | _   | 18.0  | 20.0 |      |

|                   | DRATE = L | I <sub>dd6</sub> | DS = Continual Input |     | 33.0  | 37.0 | ]    |

|                   | DRATE = H | I <sub>dd7</sub> |                      | _   | 18.0  | 20.0 |      |

$<sup>^{\</sup>star}$  625  $\mu s$  burst/5 ms period (DRATE = L) at DCLK = 384 kHz. 6.6 ms burst/20 ms period (DRATE = H) at DCLK = 42 kHz.

# ANALOG CHARACTERISTICS $(T_A = 25^{\circ}C)$

| Parameters              |                       | Symbol                  | Condition                          | Min   | Тур** | Max | Unit   |

|-------------------------|-----------------------|-------------------------|------------------------------------|-------|-------|-----|--------|

| Output Swing Level      | V <sub>DD</sub> = 3 V | V <sub>out</sub>        | $RL = k\Omega$ , $TXD = L$         | 500   | 550   | 600 | mV p-p |

| I/Q Out                 | V <sub>DD</sub> = 5 V |                         | Normal Mode                        | 520   | 570   | 620 |        |

| Output Swing Imbalance  |                       | ΔV <sub>out</sub>       |                                    | - 0.5 | 0     | 0.5 | dB     |

| Output DC Level         | V <sub>DD</sub> = 3 V | V <sub>out</sub>        | DS = L                             | 800   | 820   | 840 | mV     |

| I/Q Out                 | V <sub>DD</sub> = 5 V |                         |                                    | 780   | 800   | 820 | 1      |

| Output Swing Imbalance  |                       | $\Delta V_{	extsf{DD}}$ |                                    | _     | _     | 20  | ]      |

| Out-of-Band Noise Level | V <sub>DD</sub> = 5 V | V <sub>in</sub>         | 600 kHz                            | _     | - 50  | _   | dB     |

|                         |                       |                         | 900 kHz                            | _     | - 55  | _   | 1      |

| DC Output Resistance    |                       | R <sub>out</sub>        | I <sub>out</sub> /Q <sub>out</sub> | _     | 50    | 100 | Ω      |

<sup>\*</sup>DAref1 = H at  $V_{DD}$  = 3 V, DAref3 = H at  $V_{DD}$  = 5 V

MOTOROLA MC145750

<sup>\*\*</sup> Typical numbers are not guaranteed.

<sup>\*\*</sup> Typical numbers are not guaranteed.

# SWITCHING CHARACTERISTICS $(T_A = 25^{\circ}C)$

| Parameters                    |                       | Symbol          | Condition                           | Min                   | Typ* | Max                   | Unit |

|-------------------------------|-----------------------|-----------------|-------------------------------------|-----------------------|------|-----------------------|------|

| Input Voltage                 | High-Level            | VIH             |                                     | V <sub>DD</sub> x 0.7 | _    | _                     | V    |

|                               | Low-Level             | V <sub>IL</sub> |                                     | _                     | _    | V <sub>DD</sub> x 0.3 |      |

| Output Voltage                | High-Level            | Voн             | BW, PNO                             | V <sub>DD</sub> x 0.9 | _    | _                     |      |

|                               | Low-Level             | VOL             |                                     | _                     | _    | V <sub>DD</sub> x 0.1 |      |

| Data Set-Up Time              |                       | t <sub>su</sub> | TXD, DS, STBY                       | 10                    | _    | _                     | ns   |

| Data Hold Time                |                       | <sup>t</sup> h  | TXD, DS, STBY                       | 10                    | _    | _                     |      |

| Data Output Propagation Delay |                       | t <sub>pd</sub> | BW, PNO                             | _                     | 1.5  | 3                     | μs   |

| I/Q Output Propagation Delay  | /                     | T <sub>D</sub>  | I <sub>out</sub> , Q <sub>out</sub> | _                     | 4    | 6                     |      |

| Data Rate                     | V <sub>DD</sub> = 3 V |                 | DRATE = L                           | _                     | _    | 450                   | kbps |

|                               |                       |                 | DRATE = H                           | _                     | _    | 55                    |      |

|                               | V <sub>DD</sub> = 5 V |                 | DRATE = L                           | _                     | _    | 800                   |      |

|                               |                       |                 | DRATE = H                           | _                     | _    | 100                   |      |

| Clock Input Duty Cycle        |                       | DCLK            |                                     | 45                    | 50   | 55                    | %    |

| VCO Oscillation Frequency     | V <sub>DD</sub> = 3 V | fVCO1           |                                     | _                     | _    | 20                    | MHz  |

|                               | V <sub>DD</sub> = 5 V | fVCO2           |                                     | _                     | _    | 32                    |      |

<sup>\*</sup> Typical numbers are not guaranteed.

Figure 1. Timing Diagram

#### PIN DESCRIPTIONS

#### **POWER SUPPLY**

# Vss

#### Digital Ground (Pins 6, 44)

These are the negative power supply input pins to the digital portion of the device and are connected to ground (0 V).

#### $V_{DD}$

#### Positive Power Supply Input (Pins 7, 43)

These are the positive power supply input pins to the digital portion of the device. Typical operating voltage range is 3.3 V at DAref3 = H, 5.0 V at DAref1 = H. Power should be fed simultaneously with DAV<sub>DD</sub> pin in order to avoid any possible damage to the device.

# DAVDD

# Positive Power Supply Input for DACs (Pin 13)

This is the positive power supply input pin to the analog portion of the device. Typical operating voltage range is 2.7 V to 5.5 V.

#### DAVSS

# Analog Ground for DACs (Pin 14)

This is the negative power supply pin to the analog portion of the device and is connected to ground.

#### MODE CONTROL AND TEST

#### MODE0 - MODE2

# Normal/Test Mode Select (Pins 1, 2, 3)

These pins must be connected to ground for normal operation. For system test, PN pattern generation mode will be performed when MODE0 = H and MODE1, MODE2 = L. PN511 signal is fed to the encoder instead of input data from TXD pin. Data shift timing is the same as the normal operation mode and burst timing indicated by DS pin is still valid for the device. The PN511 signal is monitored at the PNO pin.

# **TEST**

#### Test Mode (Pin 4)

The device operates normally while this pin is held low. When this signal is high, the device enters into factory test mode. Only one mode is allowed to be enacted by user for PN Mode.

# **DRATE**

#### Data-Rate Select (Pin 9)

This pin can select high data rate when it is low, such as in PHS applications.

# **QPSK**

#### (D)QPSK/\pi/4-Shift QPSK Mode Select (Pin 10)

The device operates as a  $\pi/4$ –QPSK Encoder when this pin is held high. By making this pin low, it functions as non–shift differential QPSK Encoder. All of the functions are the same in both modes.

#### PN0/TB8

#### PN511 Test Pattern Output/Test Bus 8 (Pin 23)

This is the output data of PN511 test–pattern in normal mode. When the PN pattern generator outputs to this pin, it can be output I/Q pins and data from TXD pin may be ignored. If the DS signal is L, I/Q pins stop but PN data stream may be output.

#### **TB0 - TB7**

# Test Bus (Pins 24, 26 - 32)

These pins are used in factory test and should be connected to ground for normal operation.

#### **PLL**

# Int/Ext PLL Clock Select (Pin 41)

When this pin is connected to ground, the PLL is active and timing will be generated internally. When this pin is connected to VDD, timing should be applied to the ECLK pin.

#### **DIGITAL INTERFACE PINS**

#### RW/TR9

#### **Burst Window Output/Test Bus 9 (Pin 22)**

This output indicates when modulated baseband I/Q signals are output from this device. This pin is used as the transmission control signal for saving power for RF.

#### **ECLK**

#### **External Clock Input (Pin 42)**

When the internal timing generator with PLL is not used in the system, this pin must have 15.36 MHz applied as a system clock for this device. This pin is connected to ground for normal operation.

#### **DCLK**

#### **Data Shift Clock Input (Pin 45)**

This is the shift clock input for the transmit data input and is typically 384 kHz for the PHS (DRATE Pin = L) and 42 kHz for the PDC (DRATE Pin = H) application. The data input occurs at the rising edge of the DCLK. For burst–type systems such as the TDMA data transmission applications, this signal must be synchronized with the rising/falling edge of the DS pin (Data Slot Timing Input).

# **DS/STBY**

# **Data Slot Timing/Standby Input (Pin 46)**

For burst-type, this input signal indicates when transmit data are valid for the device. Its duration must be equal with the number of input data to the device, and its transition must be aligned with the rising edge of the DCLK signal.

When a logic L is applied to this pin, all digital portions except the timing generator are not clocked and the device is in a low power dissipation mode. When a logic H is applied continuously, all input data are encoded as valid data.

#### TXD

# **Transmit Data Input (Pin 47)**

Data bit streams to be transmitted are input to this pin. The data is valid only when the DS (Pin 46) is asserted (high). Its transition should be synchronized with rising edge of the DCLK (Pin 45).

MOTOROLA MC145750

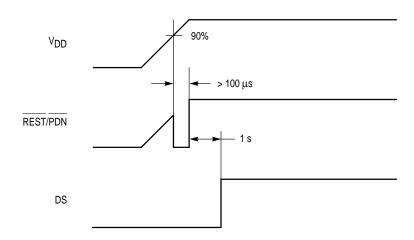

#### **ERST/PDN**

# External Reset/Power Down Input (Pin 48)

When a logic L is applied to this pin, it forces a complete power down. When at start up, V<sub>DD</sub> goes high, it is recommended that a logic L, then a logic H be applied to this pin to start up and reset all digital portions.

#### **ANALOG INTERFACE PINS**

# Qout

#### Filtered Quadrature-Phase Output (Pin 15)

This is the modulated quadrature–phase signal output and the amplitude is typically 550 mV p–p at  $V_{DD} = 3$  V in PN test mode. The output dc resistance is approximately 50  $\Omega$ .

# lout

# Filtered In-Phase Output (Pin 20)

This is the modulated in–phase signal output and amplitude is typically 500 mV p–p at V<sub>DD</sub> = 3 V in PN test mode. The output dc resistance is approximately 50  $\Omega$ .

#### DAC AND PLL SETTING

#### DAb

# Reference Bias Setting Pin to DACs (Pin 12)

A resistor connected to ground from this pin determines the reference current value for internal DACs. This resistor's value is 200 k $\Omega$  typically.

#### **DAref**

#### Ripple Filter Capacitor (Pin 16)

A capacitor connected to ground from this pin acts as a ripple filter for the internal DACs' reference voltage. This capacitor's value is  $0.1\mu F$ , typically.

# DAref1 - DAref3

# Reference Bias Setting to DACs (Pin 17 - 19)

These pins determine the reference voltage for internal DACs in conjunction with DAb pin. At 3 V operation, DAref1 pin should be connected to  $V_{DD}$ . DAref2 pin should be connected to  $V_{DD}$  at 3.3 V. DAref3 pin should be connected to  $V_{DD}$  at 5 V. The two other pins for the respective cases must be left open.

#### **PB1. PB2**

# **PLL Bias (Pins 35, 38)**

This pin determines the bias of the PLL. Its recommended values are shown in Table 1 and it depends on operating voltage.

#### Cf

#### Loop Filter Capacitor (Pin 39)

Input from Cf pin is fed directly as the internal VCO control signal.

#### **PCO**

### **Phase Comparator Output (Pin 40)**

Connect an LPF as loop filter for the PLL. Refer to the application figure for recommended values.

**Table 1. Function Table**

|    | Pin      | L                     | н                     | Remarks                                                                                                                                                                                           |  |

|----|----------|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3  | MODE0    | Normal Mode           | PN Pattern            | These settings are independent of power supply.                                                                                                                                                   |  |

| 10 | QPSK     | Non-Shift             | /4–Shift              |                                                                                                                                                                                                   |  |

| 9  | DRATE    | High Speed            | Low Speed             | To be determined setting high or low speed data rate.                                                                                                                                             |  |

| 17 | DAref1   | _                     | V <sub>DD</sub> = 5 V | These pins should be held high depending on power supply voltage                                                                                                                                  |  |

| 18 | DAref2   | _                     | V <sub>DD</sub> 3.3 V | others should be left open.                                                                                                                                                                       |  |

| 19 | DAref3   | _                     | V <sub>DD</sub> 3.0 V |                                                                                                                                                                                                   |  |

| 41 | PLL      | PLL Operation<br>Mode | Ext Clock Mode        | In case of external clock mode, TX data rate must be set to a frequency of 1/40 when DRATE = L, and must be set to a frequency of 1/320 when DRATE = H. Max data rate is limited by power supply. |  |

| 48 | ERST/PDN | Power Down            | Normal Operation      | Digital circuits reset condition will be released by rising edge of this input.                                                                                                                   |  |

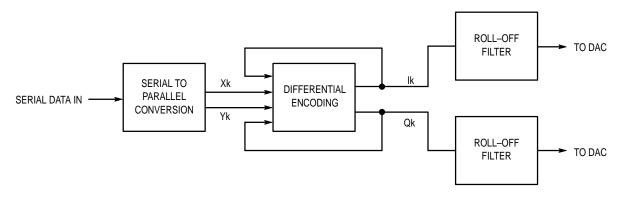

Figure 2. DQPSK Baseband Signal Generation

#### **DEVICE DESCRIPTION**

#### π/4−Shift QPSK Encoding

RCR standard (STD–28) specifies the basic configuration of this modulation scheme as shown in Figure 2. First, serial data input is converted to Xk/Yk parallel streams. Then its value is compared with one previous symbol Ik/Qk, respectively, whether or not there is a change of polarity. If there is a change, result is coded as 1. This two–bit  $\pi r$  (di–bit) is called symbol, hence symbol rate is just half of the data input rate to be modulated.

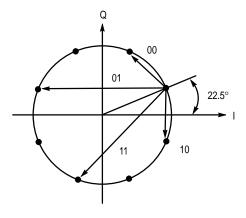

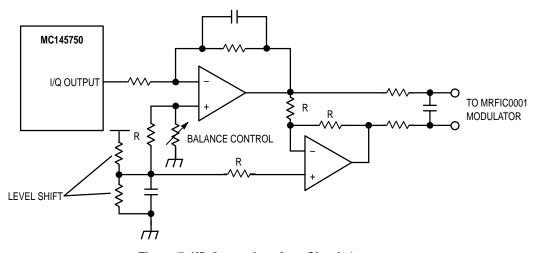

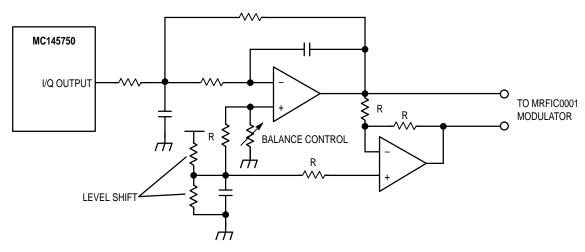

Phase transitions are determined as shown in Figure 3, with respect to four di–bit values of Xk, Yk. (As is shown, there should be at least  $\pi/4$  of phase shift in each symbol timing unlike plain QPSK.) Actual in–phase outputs are fed to a quadrature modulator circuit, and it is recommended that a 2– to 3–order LPF be used, which may be used as a level shifter and dc offset compensation circuitry at the same time.

The reference voltage for the DACs is given by connecting either of DAref1:3 to V<sub>DD</sub> according to the operating voltage used. It is preferable not to have this voltage vary, since I/Q output levels are affected.

# **Timing Generator**

The PLL is intended in order to generate all required timing signals for the devices. The VCO oscillating at the PN511 pattern rate is utilized when some characteristics are measured. By pulling MODE0 pin high, the device generates this sequence. It is a useful simple measurement for the occupied power bandwidth and the out–of–band power level. The sequence itself can also be monitored at the PNO pin.

This circuit is reset by an external reset signal while the low-state of DS is not valid for initializing the generator.

# START-UP SEQUENCE

To ensure stability and to initialize the internal ROM and encoder, the start-up sequence should be done at power-up. Refer to Figure 4.

# Di-Bit Input

| Xk | Yk | Phase Shift |

|----|----|-------------|

| 0  | 0  | π/4         |

| 0  | 1  | 3π/4        |

| 1  | 0  | $-\pi/4$    |

| 1  | 1  | $-3\pi/4$   |

Figure 3. Phase Diagram

Figure 4. Start-Up Sequence

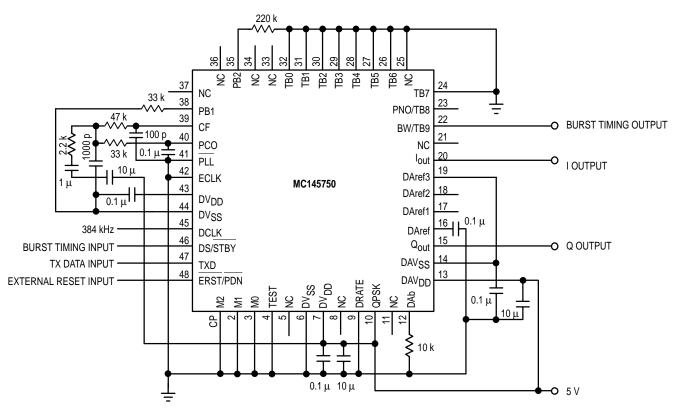

Figure 5. DRATE Equals L: 5 V Operation

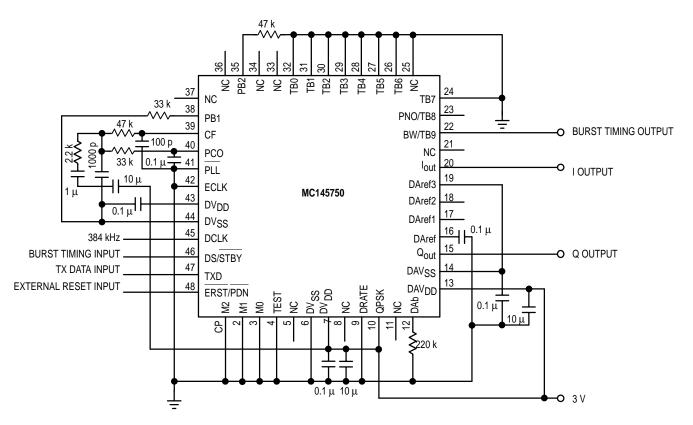

Figure 6. DRATE Equals H: 3 V Operation

Figure 7. I/Q Output Interface Circuit 1

Figure 8. I/Q Output Interface Circuit 2

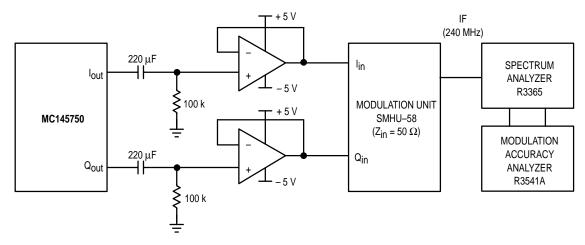

Measurement Equipment: Advantest Spectrum Analyzer R3365

Advantest Modulation Accuracy Analyzer R3541A Rohde & Schwarz Modulation Unit SMHU–58

Conditions: Internal PLL mode, 384 kbps (PHS),  $T_A = 25^{\circ}C$

Motorola cannot recommend one supplier over another and in no way suggests that this is a complete listing of measurement equipment suppliers.

Figure 9. Modulation Accuracy Measurement Schematic

MOTOROLA MC145750

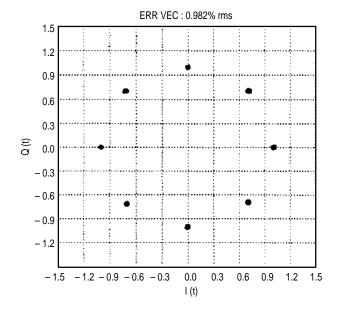

Figure 10. I-Q Pattern

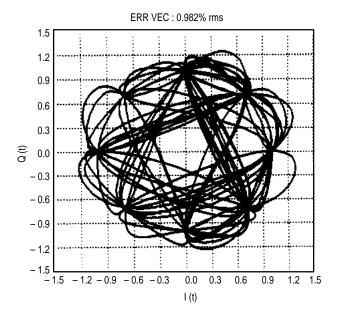

Figure 11. I-Q Pattern

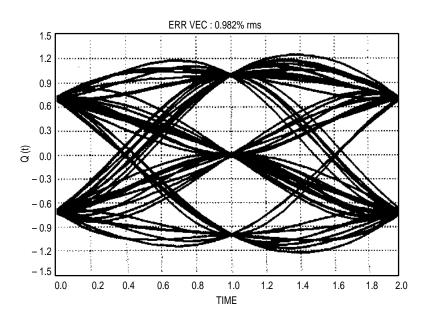

Figure 12. Q-Eye Pattern

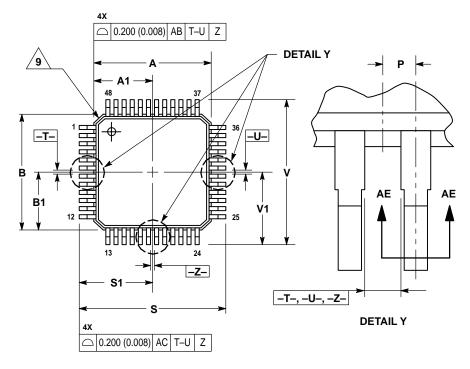

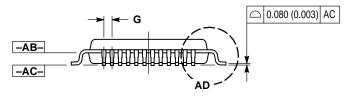

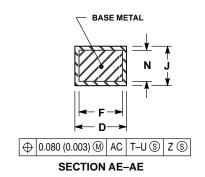

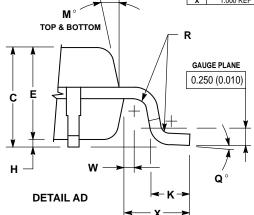

# **PACKAGE DIMENSIONS**

# **VFU SUFFIX** PLASTIC VQFP CASE 932-02

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DATUM PLANE -AB- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

4. DATUMS -T-, -U-, AND -Z- TO BE DETERMINED AT DATUM PLANE -AB-.

5. DIMENSIONS S AND V TO BE DETERMINED AT SFATING PI ANF -AC-

- DIMENSIONS 3 AND VIO BE DETERMINED AT SEATING PLANE -AC-.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.250 (0.010) PER SIDE. DIMENSIONS A AND B DO U.230 (U.10) PER SIDE: DIMENSIONS A AND BI INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -AB-. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL

- NOT CAUSE THE D DIMENSION TO EXCEED

- 0.350 (0.014).

8. MINIMUM SOLDER PLATE THICKNESS SHALL BE

- 0.0076 (0.0003). 9 EXACT SHAPE OF EACH CORNER IS OPTIONAL.

|     | MILLIN | IETERS | INC     | HES   |  |

|-----|--------|--------|---------|-------|--|

| DIM | MIN    | MAX    | MIN     | MAX   |  |

| Α   | 7.000  | BSC    | 0.276   | BSC   |  |

| A1  | 3.500  | BSC    | 0.138   | BSC   |  |

| В   | 7.000  | BSC    | 0.276   | BSC   |  |

| B1  | 3.500  | BSC    | 0.138   | BSC   |  |

| С   | 1.400  | 1.600  | 0.055   | 0.063 |  |

| D   | 0.170  | 0.270  | 0.007   | 0.011 |  |

| E   | 1.350  | 1.450  | 0.053   | 0.057 |  |

| F   | 0.170  | 0.230  | 0.007   | 0.009 |  |

| G   | 0.500  | BASIC  | 0.020   | BASIC |  |

| Н   | 0.050  | 0.150  | 0.002   | 0.006 |  |

| J   | 0.090  | 0.200  | 0.004   | 0.008 |  |

| K   | 0.500  | 0.700  | 0.020   | 0.028 |  |

| M   | 12°    | REF    | 12 °REF |       |  |

| N   | 0.090  | 0.160  | 0.004   | 0.006 |  |

| P   |        | BASIC  |         | BASIC |  |

| Q   | 1°     | 5°     | 1°      | 5°    |  |

| R   | 0.150  | 0.250  | 0.006   | 0.010 |  |

| S   | 9.000  | BSC    | 0.354   | BSC   |  |

| S1  | 4.500  | BSC    | 0.177   | BSC   |  |

| ٧   | 9.000  | BSC    | 0.354   | BSC   |  |

| V1  | 4.500  | BSC    | 0.177   | BSC   |  |

| W   | 0.200  | REF    | 0.008   | REF   |  |

| Х   | 1.000  | REF    | 0.039   | REF   |  |

**MOTOROLA** MC145750

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and "a are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

**USA/EUROPE**: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE (602) 244–6609 INTERNET: http://Design-NET.com

**JAPAN**: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

**HONG KONG**: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298